## **EXPERIMENT NO. 1: CHARACTERIZATION OF DIODE CIRCUITS**

### 1.0 AIM:

The primary aim of this experiment is to thoroughly investigate the electrical characteristics of fundamental semiconductor diodes (PN junction and Zener diodes) and to understand their application in basic power conversion circuits (rectifiers and voltage regulators).

## 2.0 OBJECTIVES:

Upon successful completion of this experiment, you will be able to:

- Plot and interpret the Current-Voltage (I-V) characteristics of a PN junction diode in both forward and reverse bias.

- Determine the cut-in voltage of a silicon PN junction diode.

- Plot and interpret the I-V characteristics of a Zener diode in reverse bias.

- Determine the Zener breakdown voltage (V Z) of a Zener diode.

- Construct and analyze the operation of a half-wave rectifier circuit.

- Construct and analyze the operation of a full-wave bridge rectifier circuit, both with and without a filter capacitor.

- Measure and compare the DC output voltage and ripple voltage for different rectifier configurations.

- Design and implement a simple Zener diode voltage regulator.

- Evaluate the line and load regulation performance of the Zener regulator.

- Effectively use laboratory equipment such as the DC power supply, AC function generator, Digital Multimeter (DMM), and Oscilloscope for circuit analysis.

## 3.0 APPARATUS REQUIRED:

| S.<br>No. | Component/Equipment           | Specifications/Value         | Quantity |

|-----------|-------------------------------|------------------------------|----------|

| 1.        | DC Power Supply<br>(Variable) | 0-30V, Dual Output           | 1        |

| 2.        | AC Function Generator         | Sine wave, 0-20Vp-p, 50Hz    | 1        |

| 3.        | Digital Multimeter (DMM)      | Voltage, Current, Resistance | 2        |

| 4.        | Oscilloscope                  | Dual Trace, 20MHz bandwidth  | 1        |

| 5.        | Breadboard                    | Standard Size                | 1        |

| 6.        | Diode (PN Junction)           | 1N4007                       | 5        |

| 7.        | Zener Diode                   | e.g., 5.1V, 0.5W             | 1        |

| 8.  | Resistors                 | 100 Ω, 470 Ω, 1 kΩ, 10 kΩ                            | As<br>needed |

|-----|---------------------------|------------------------------------------------------|--------------|

| 9.  | Capacitors (Electrolytic) | 100 μF, 470 μF (25V/50V)                             | 1 each       |

| 10. | Step-down Transformer     | 230V AC Primary to 6V-0-6V or 12V-0-12V AC Secondary | 1            |

| 11. | Connecting Wires          | Assorted                                             | As<br>needed |

Export to Sheets

## 4.0 THEORY AND FUNDAMENTALS:

This section provides a detailed theoretical background for each part of the experiment, including relevant formulas and explanations.

## 4.1 The PN Junction Diode: The Unidirectional Valve

A PN junction diode is a two-terminal semiconductor device formed by joining P-type and N-type semiconductor materials. Its primary characteristic is to allow current flow predominantly in one direction.

Structure: The P-type material has an abundance of holes (positive charge carriers),

while the N-type material has an abundance of free electrons (negative charge

carriers). At the junction, electrons and holes combine, creating a depletion region

devoid of mobile charge carriers and establishing a built-in electric field (barrier

potential).

## • Forward Bias Operation:

- **Connection:** The positive terminal of an external voltage source is connected to the P-side (anode), and the negative terminal to the N-side (cathode).

- Effect: The external voltage opposes the built-in potential barrier. As the forward voltage (V\_D) increases, the depletion region narrows, and eventually, the majority carriers (holes from P-side, electrons from N-side) gain enough energy to cross the barrier.

- Conduction: Once V\_D exceeds a certain threshold voltage, known as the cut-in voltage (or knee voltage, or turn-on voltage, V\_F), the diode begins to conduct significant current.

- For silicon diodes, V\_F is typically between 0.6V and 0.7V.

- For germanium diodes, V F is typically around 0.2V to 0.3V.

- I-V Relationship (Shockley Diode Equation): The relationship between diode current (I\_D) and diode voltage (V\_D) in forward bias is described by: I\_D=I\_Sleft(efracV\_DetaV\_T-1right) Where:

- I\_D: Diode current (Amperes)

- I\_S: Reverse saturation current (A), a very small leakage current, highly temperature-dependent.

- V\_D: Voltage across the diode (Volts)

- eta: Ideality factor (dimensionless), typically ranges from 1 to 2

(approx. 1 for germanium, 2 for silicon at low currents, approaches 1

at higher currents). It accounts for deviations from ideal behavior.

- V\_T: Thermal voltage (Volts), given by V\_T=frackTq

- k: Boltzmann's constant (1.38times10-23 J/K)

- T: Absolute temperature of the junction in Kelvin (e.g., \$27^\\circ C = 300 K\$)

- q: Magnitude of electron charge (1.602times10-19 C)

- At room temperature (\$27^\\circ C\$ or 300K),

V Tapprox25.85textmVapprox26textmV.

- Approximation: For V\_DggetaV\_T (which is true when the diode conducts significantly), the −1 term becomes negligible, and the equation simplifies to: I\_DapproxI\_SefracV\_DetaV\_T. This shows the exponential increase in current once the cut-in voltage is surpassed.

## • Reverse Bias Operation:

- Connection: The positive terminal of the external voltage source is connected to the N-side (cathode), and the negative terminal to the P-side (anode).

- **Effect:** The external voltage adds to the built-in potential barrier. The depletion region widens, effectively blocking the flow of majority carriers.

- Conduction: Only a very small leakage current, the reverse saturation current (I\_S), flows due to the thermally generated minority carriers crossing the junction. This current is typically in the nanoampere (nA) or picoampere (pA) range for silicon diodes.

- Breakdown: If the reverse voltage increases beyond a certain limit, called the reverse breakdown voltage (V\_BR), the diode undergoes avalanche or Zener breakdown, leading to a sharp and rapid increase in reverse current. This region is typically avoided for standard rectification as it can permanently damage the diode unless current is strictly limited.

## 4.2 The Zener Diode: The Voltage Regulator

A Zener diode is specifically designed to operate reliably and safely in the reverse breakdown region. Its key feature is that it maintains a nearly constant voltage across its terminals when reverse biased beyond its breakdown point, making it ideal for voltage regulation.

• **Forward Bias:** In forward bias, a Zener diode behaves just like a regular PN junction diode, with a cut-in voltage of around 0.7V for silicon.

## • Reverse Bias and Zener Breakdown:

- When reverse biased, initially a small leakage current flows, similar to a standard diode.

- As the reverse voltage increases, it eventually reaches the Zener voltage

(V Z), at which point the diode enters the breakdown region.

- In the breakdown region, the voltage across the Zener diode remains remarkably constant at V\_Z, even if the current flowing through it (I\_Z) varies significantly (within the specified operating limits). This characteristic is due to either:

- **Zener breakdown:** Occurs in heavily doped junctions, where a strong electric field causes electrons to tunnel directly from the valence band to the conduction band. Predominant for \$V\ Z \< 5V\$.

- Avalanche breakdown: Occurs in lightly doped junctions, where minority carriers gain enough energy to collide with atoms, knocking out more electrons, leading to a cumulative multiplication of charge carriers. Predominant for V\_Z6V.

- Power Dissipation: It is crucial to limit the current through the Zener diode using a series resistor to prevent its power dissipation (P\_Z=V\_ZtimesI\_Z) from exceeding its maximum power rating, which would lead to overheating and damage.

## 4.3 Rectifier Circuits: Converting AC to Pulsating DC

Rectifiers are essential circuits that convert alternating current (AC) into pulsating direct current (DC). This is the first step in converting AC mains power into usable DC for electronic devices.

### 4.3.1 Half-Wave Rectifier

The simplest rectifier, using only one diode.

- Circuit Diagram: (See Figure 4 in Procedure section)

- Operation:

- During the positive half-cycle of the AC input voltage, the anode of the diode becomes positive with respect to its cathode. If the peak input voltage exceeds the diode's cut-in voltage (V\_F), the diode becomes forward-biased and conducts. Current flows through the load resistor (R\_L), and the output voltage across R\_L closely follows the input voltage minus V\_F.

- During the **negative half-cycle**, the cathode of the diode becomes positive

with respect to its anode. The diode is reverse-biased and effectively acts as

an open circuit, blocking current flow. Thus, the output voltage across R\_L is

approximately zero.

- Key Parameters (Ideal Diode Assumption, V\_F=0V):

- Peak Output Voltage (V\_p(out)): V\_p(out)=V\_m (where V\_m is the peak AC input voltage from the transformer secondary). For practical diodes, V\_p(out)=V\_m-V\_F.

- Average (DC) Output Voltage (V\_DC): This is the average value of the rectified output waveform. V\_DC=fracV\_mpiapprox0.318V\_m For practical diodes, V\_DC=fracV\_m-V\_Fpi.

- Peak Inverse Voltage (PIV): This is the maximum reverse-bias voltage that the diode must withstand when it is not conducting. PIV=V m

- Ripple Frequency (f\_ripple): The frequency of the pulsations in the DC output. f\_ripple=f\_in (where f\_in is the input AC frequency, e.g., 50 Hz for mains).

#### Disadvantages:

- o Inefficient use of input AC cycle (only half is utilized).

- High ripple content, making filtering more difficult.

Low average DC output voltage.

## 4.3.2 Full-Wave Bridge Rectifier

A more efficient rectifier configuration that utilizes both half-cycles of the AC input. It typically uses four diodes.

- Circuit Diagram: (See Figure 5 in Procedure section)

- Operation:

- During the positive half-cycle of the AC input: Current flows from the transformer secondary, through diode D1, through the load resistor (R\_L), through diode D2, and back to the transformer. Both D1 and D2 are forward-biased.

- During the negative half-cycle of the AC input: Current flows from the opposite end of the transformer secondary, through diode D3, through the load resistor (R\_L) in the same direction as before, through diode D4, and back to the transformer. Both D3 and D4 are forward-biased.

- In both half-cycles, current flows through the load resistor in the same direction, resulting in a pulsating DC output that is always positive (or always negative, depending on diode orientation).

- Key Parameters (Ideal Diode Assumption, V\_F=0V):

- Peak Output Voltage (V\_p(out)): V\_p(out)=V\_m. For practical diodes, since two diodes are in series for conduction during each half-cycle, V\_p(out)=V\_m-2V\_F.

- Average (DC) Output Voltage (V\_DC): V\_DC=frac2V\_mpiapprox0.636V\_m

For practical diodes, V\_DC=frac2(V\_m-2V\_F)pi.

- Peak Inverse Voltage (PIV): PIV=V\_m (each diode must withstand V\_m when it is reverse biased).

- **Ripple Frequency (f\_ripple):** f\_ripple=2f\_in (e.g., 100 Hz for 50 Hz mains). This higher ripple frequency makes filtering easier.

## Advantages:

- Higher average DC output voltage compared to half-wave.

- Lower ripple content and higher ripple frequency, making filtering more effective.

- More efficient use of the input AC cycle.

## 4.4 Filtering Rectifier Output: The Smoothing Capacitor

The output of both half-wave and full-wave rectifiers is pulsating DC, meaning it still contains significant AC components (ripple). For most electronic applications, a smooth, nearly constant DC voltage is required. A filter capacitor is commonly used to "smooth out" these pulsations.

- Operation with Capacitor: A large electrolytic capacitor (C) is connected in parallel with the load resistor (R\_L) at the rectifier output.

- During the peaks of the rectified voltage, the capacitor charges rapidly to the peak voltage (V\_p(out)).

- When the rectified voltage falls below the capacitor voltage (i.e., the diode becomes reverse biased), the capacitor begins to discharge slowly through

- the load resistor, maintaining a relatively high voltage across the load until the next rectified peak.

- This charging and discharging action reduces the voltage fluctuations, resulting in a much smoother DC output with reduced ripple.

- **Ripple Voltage (V\_r):** The peak-to-peak ripple voltage is approximately given by: V\_rapproxfracl\_DCf\_rippleC or V\_rapproxfracV\_DCf\_rippleR\_LC Where:

- I\_DC: Average DC load current

- o V DC: Average DC output voltage

- o f\_ripple: Ripple frequency (e.g., f\_in for half-wave, 2f\_in for full-wave)

- o R L: Load resistance

- o C: Filter capacitance

- **DC Output Voltage (with filter):** The average DC output voltage with a filter capacitor will be approximately V\_p(out)-fracV\_r2. Ideally, it approaches V\_p(out).

## 4.5 Zener Voltage Regulator: Stabilizing the DC Output

While a filter capacitor reduces ripple, it doesn't provide precise voltage regulation against variations in input voltage (line regulation) or load current (load regulation). A Zener diode can be used to achieve this.

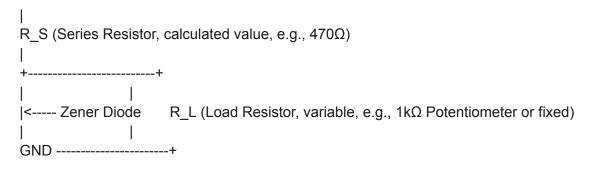

- **Circuit Diagram:** (See Figure 7 in Procedure section)

- Operation:

- A current-limiting series resistor (R\_S) is connected between the unregulated DC input voltage (V in) and the Zener diode.

- The Zener diode is connected in parallel with the load (R\_L) and is reverse-biased.

- When V\_in is applied, it causes current to flow through R\_S. If V\_in is sufficiently high to push the Zener diode into its reverse breakdown region, the voltage across the Zener diode (and thus across the load, V\_out) stabilizes at V\_Z.

- The total current from the source (I\_S) divides between the Zener diode (I\_Z) and the load (I\_L): I\_S=I\_Z+I\_L.

- The voltage drop across R\_S is V\_RS=V\_in-V\_Z.

## Regulation Mechanism:

- Line Regulation (Input Voltage Variation): If V\_in increases, I\_S (current through R\_S) increases. The excess current flows through the Zener diode (I\_Z), while V\_Z (and V\_out) remains constant. Similarly, if V\_in decreases, I\_Z decreases, maintaining constant V\_out.

- Load Regulation (Load Current Variation): If the load current (I\_L) increases, the Zener current (I\_Z) decreases to compensate, keeping I\_S (and thus V\_out) relatively constant. If I\_L decreases, I\_Z increases.

## Design Considerations for R\_S:

- R\_S must be chosen such that the Zener diode is always in its breakdown region under varying load and input conditions.

- The maximum Zener current (I\_ZM) should not be exceeded.

- The minimum Zener current (I\_ZK, knee current) must be maintained to ensure proper regulation.

- A common approach for calculating R\_S:

R\_S=fracV\_in(min)-V\_ZI\_Z(min)+I\_L(max).

- Regulation Metrics:

- Load Regulation (%): Measures the change in output voltage from no-load to full-load conditions. Load Regulation (Where V\_NL is the no-load output voltage (I\_L=0) and V\_FL is the full-load output voltage (I\_L=I\_L(max)). A lower percentage indicates better regulation.

- Line Regulation (%): Measures the change in output voltage due to a change in input voltage. Line Regulation (A lower percentage indicates better regulation.

## **5.0 CIRCUIT DIAGRAMS:**

## Figure 1.1: PN Junction Diode Forward Bias Setup

```

+V_in (DC Supply)

R1 (Current Limiting Resistor, e.g., 1kΩ)

+---->|---- GND (Ground)

Diode (1N4007)

(Anode to R1, Cathode to GND)

V_D (measure across diode with DMM)

I_D (measure current through R1, I_D = (V_in - V_D)/R1, or use DMM in current mode in series)

```

## Figure 1.2: PN Junction Diode Reverse Bias Setup

```

+V_in (DC Supply)

|

R1 (Current Limiting Resistor, e.g., 1kΩ)

|

+----|<---- GND (Ground)

Diode (1N4007)

(Cathode to R1, Anode to GND)

|

V_R (measure across diode with DMM)

I_R (measure current through R1)

```

Figure 1.3: Zener Diode Reverse Bias Setup

```

+V_in (DC Supply) | R_S (Series Resistor, e.g., 470\Omega - 1k\Omega)

```

```

|

+----|<---- GND (Ground)

Zener Diode

(Cathode to R_S, Anode to GND)

|

V_Z (measure across Zener with DMM)

I_Z (measure current through R_S)

```

Figure 1.4: Half-Wave Rectifier Circuit

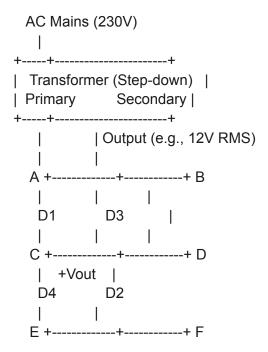

Figure 1.5: Full-Wave Bridge Rectifier Circuit (Unfiltered)

```

R_L (Load Resistor, e.g., 1kΩ)

| GND

(Diodes: D1, D2, D3, D4 - 1N4007)

(A,B,C,D,E,F are connection points for clarity. Transformer secondary connects between A and F)

(Output is taken between point C (+Vout) and point D (GND))

Bridge Connections:

Anode D1 to A, Cathode D1 to C

Anode D3 to D, Cathode D3 to B

Anode D4 to F, Cathode D4 to C

Anode D2 to D, Cathode D2 to B

(Connect Oscilloscope Channel 1 across transformer secondary (A to F) for input)

(Connect Oscilloscope Channel 2 across R_L (C to D) for output)

```

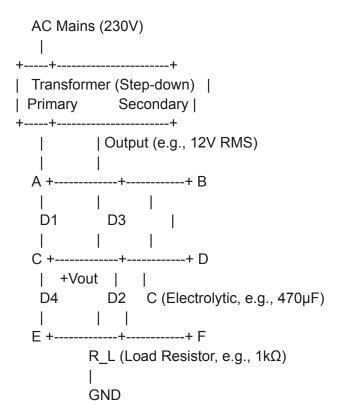

Figure 1.6: Full-Wave Bridge Rectifier Circuit (With Filter Capacitor)

(Same as Figure 1.5, but with Capacitor C in parallel with R L)

Figure 1.7: Zener Voltage Regulator Circuit

+V\_in (Regulated DC Input, from DC Power Supply)

(Measure V\_out across the Zener Diode/Load with DMM)

#### 6.0 PROCEDURE:

Perform the experiment step-by-step as outlined below. Ensure all connections are secure before powering on any circuit.

## Part A: PN Junction Diode (1N4007) Characteristics

## 1. Forward Bias Characterization:

- $\circ$  Construct the circuit shown in Figure 1.1 on the breadboard. Use a 1  $k\Omega$  resistor for R 1.

- Set the DC Power Supply to its minimum voltage (0V).

- Connect the DMM in voltage mode across the diode to measure V\_D.

- Connect another DMM in current mode in series with the diode and resistor to measure I\_D. Alternatively, measure the voltage across the 1 kΩ resistor (V R1) with a DMM, and calculate I D=V R1/1kΩ.

- Slowly increase the input voltage (V\_in) from 0V.

- Record pairs of (V\_D,I\_D) readings. Initially, take readings in small increments (e.g., 0.05V or 0.1V) around the expected cut-in voltage (0.5V to 0.7V for silicon). After the diode starts conducting significantly, larger increments (e.g., 0.5V) are fine.

- Continue taking readings until the diode current reaches about 15-20 mA (or the maximum safe current for the 1N4007).

- Record your observations in Observation Table 1.1.

## 2. Reverse Bias Characterization:

- Modify the circuit by reversing the diode connection as shown in Figure 1.2.

- Ensure the power supply voltage is at 0V before making changes.

- Increase the reverse input voltage (V in) in steps (e.g., 1V increments).

- Record the reverse voltage across the diode (V\_R) and the corresponding reverse current (I\_R). Note that I\_R will be very small (in microamperes or nanoamperes) for a 1N4007 diode before breakdown.

- Do not exceed the maximum reverse voltage rating of the 1N4007 diode (typically 50V to 1000V, check datasheet for specific 1N400x). Do NOT attempt to reach the breakdown voltage of a standard rectifier diode, as it can damage it.

- Record your observations in Observation Table 1.1.

## Part B: Zener Diode Characteristics

## 1. Reverse Bias Characterization:

- $\circ$  Construct the circuit shown in Figure 1.3 on the breadboard. Use a Zener diode (e.g., 5.1V) and a series resistor (R\_S) of 470 Ω or 1 kΩ.

- Connect the Zener diode in reverse bias (cathode to the positive side of R\_S, anode to ground).

- Set the DC Power Supply to 0V.

- Connect one DMM to measure voltage across the Zener diode (V\_Z) and another DMM to measure current through R S (which is I Z).

- Slowly increase the input voltage (V\_in) from 0V.

- Record (V\_Z,I\_Z) readings in increments. Pay close attention to the region where V\_Z becomes nearly constant despite increasing I\_Z.

- Continue increasing I\_Z until it reaches a safe maximum current (e.g., 20-30 mA for a 0.5W Zener, but do not exceed the diode's power rating).

- Record your observations in Observation Table 1.2.

#### Part C: Half-Wave Rectifier Circuit

## 1. Circuit Construction:

- $\circ$  Connect the secondary winding of the step-down transformer to the diode and load resistor (R L=1k $\Omega$ ) as shown in Figure 1.4.

- Ensure the AC mains supply to the transformer primary is off initially.

- Connect Channel 1 of the Oscilloscope across the transformer secondary to observe the AC input waveform.

- Connect Channel 2 of the Oscilloscope across the load resistor (R\_L) to observe the output waveform.

- Set the oscilloscope to AC coupling for input and DC coupling for output.

Adjust Volts/Div and Time/Div settings for clear waveform visualization.

## 2. Waveform Observation:

- Switch on the AC mains supply to the transformer.

- Observe both input and output waveforms on the oscilloscope. Sketch them accurately in your observations.

- Measure the peak-to-peak voltage (V\_p-p) of the input AC waveform and calculate its peak voltage (V\_m=V\_p-p/2).

- Measure the peak voltage of the output waveform (V p(out)).

- Measure the input AC frequency and verify the output ripple frequency.

#### 3. **DC Voltage Measurement:**

- Use a DMM in DC voltage mode to measure the average DC output voltage across R\_L.

- Record all measurements in Observation Table 1.3.

# Part D: Full-Wave Bridge Rectifier Circuit

## 1. Construction (Without Filter Capacitor):

- $\circ$  Assemble the full-wave bridge rectifier circuit using four 1N4007 diodes and a 1 k $\Omega$  load resistor as shown in Figure 1.5.

- Ensure the AC mains supply to the transformer is off.

Connect the oscilloscope probes as in Part C (Channel 1 for input, Channel 2 for output across R\_L).

## 2. Waveform Observation (Without Filter):

- Switch on the AC mains supply.

- Observe and sketch both input and output waveforms.

- Measure V\_m of the input, and V\_p(out) and V\_r(p-p) of the output using the oscilloscope.

- Verify the output ripple frequency.

## 3. DC Voltage Measurement (Without Filter):

- Measure the average DC output voltage across R\_L using a DMM.

- o Record measurements in Observation Table 1.4.

## 4. Construction (With Filter Capacitor):

With the power OFF, connect an electrolytic capacitor (e.g., 470 μF, ensure correct polarity: positive to +Vout, negative to GND) in parallel with the load resistor R\_L, as shown in Figure 1.6.

## 5. Waveform Observation (With Filter):

- Switch on the AC mains supply.

- Observe the output waveform on the oscilloscope. Note the significant reduction in ripple. Sketch the new output waveform.

- Measure the peak output voltage (V\_p(out)) and the new peak-to-peak ripple voltage (V r(p-p)).

## 6. DC Voltage Measurement (With Filter):

- Measure the average DC output voltage across R\_L using a DMM.

- Record measurements in Observation Table 1.4.

## Part E: Zener Voltage Regulator Circuit

## 1. Design Calculation of Series Resistor (R\_S):

- Before building, perform the design calculation for R\_S.

- Assume your Zener diode (V\_Z from Part B, e.g., 5.1V) has a minimum operating current I\_ZKapprox1textmA and a maximum Zener current

I\_ZMapprox50textmA (typical values for 0.5W Zener).

- Assume the unregulated DC input voltage (V\_in) from your DC Power Supply will vary from a minimum (V\_in(min) = e.g., 10V) to a maximum (V\_in(max) = e.g., 15V).

- Assume your maximum load current (I\_L(max) = e.g., 10mA).

- Calculate R\_S using the formula: R\_S=fracV\_in(min)-V\_ZI\_ZK+I\_L(max).

- Choose the nearest standard resistor value for R S.

- Calculate the maximum power dissipation of the Zener diode

P\_Z=V\_ZtimesI\_Z. Here, I\_Z would be when I\_L=0 (no load) and

V\_in=V\_in(max): I\_Z=fracV\_in(max)-V\_ZR\_S. Ensure P\_Z is less than the Zener's power rating.

- o Record your design calculations.

#### 2. Circuit Construction:

- Construct the Zener voltage regulator circuit shown in Figure 1.7 on the breadboard using your calculated R\_S and chosen Zener diode.

- $\circ$  For the load resistor (R\_L), use a variable resistor (potentiometer, e.g., 10 kΩ) or a decade resistance box to simulate varying load conditions.

Connect the DMM to measure the output voltage (V\_out) across R\_L (which is equal to V\_Z).

## 3. Load Regulation Test:

- Set the input DC voltage (V\_in) to a constant value within your assumed range (e.g., 12V).

- Vary the load resistance (R\_L) from open circuit (infinite resistance) down to a minimum value that still allows the Zener to regulate (the output voltage should remain constant). This varies I\_L.

- Record R\_L, calculated I\_L (I\_L=V\_out/R\_L), and measured V\_out in Observation Table 1.5.

- Identify V\_NL (output voltage at no load, I\_L=0) and V\_FL (output voltage at maximum load current, I\_L=I\_L(max)).

- Calculate the percentage load regulation.

## 4. Line Regulation Test:

- $\circ$  Set the load resistor (R\_L) to a fixed value (e.g., 1 kΩ, or a value that draws a typical load current within your design).

- Vary the input DC voltage (V\_in) across its specified range (e.g., from 10V to 15V).

- Record V\_in and the corresponding V\_out in Observation Table 1.6.

- o Calculate the percentage line regulation.

#### 7.0 OBSERVATIONS AND READINGS:

## **Observation Table 1.1: PN Junction Diode (1N4007) Characteristics**

| S. No. | Forward Bias       |          | Reverse Bias       |          |  |

|--------|--------------------|----------|--------------------|----------|--|

|        | V_D (V) (Measured) | I_D (mA) | V_R (V) (Measured) | I_R (μA) |  |

| 1      | 0.0                | 0.0      | 0.0                | 0.0      |  |

| 2      | 0.1                |          | 1.0                |          |  |

| 3      | 0.2                |          | 2.0                |          |  |

| 4      | 0.3                |          | 5.0                |          |  |

| 5      | 0.4                |          | 10.0               |          |  |

| 6      | 0.5                |          | 20.0               |          |  |

| 7      | 0.55               |          | 30.0               |          |  |

| 8      | 0.6                |          | 40.0               |          |  |

| 9      | 0.65               |          | 50.0               |          |  |

| 10     | 0.7                |          |                    |          |  |

|        |                    |          |                    |          |  |

| Export to Sheets                                               |                                                   |                                       |                                    |  |  |

|----------------------------------------------------------------|---------------------------------------------------|---------------------------------------|------------------------------------|--|--|

| •                                                              | Observed Cut-in Voltage (                         | <b>V_F)</b> : V (from (               | graph plotting)                    |  |  |

| Obser                                                          | vation Table 1.2: Zener Dio                       | de (e.g., 5.1V) Reverse Bia           | s Characteristics                  |  |  |

| S.<br>No.                                                      | Input Voltage (V_in) (V)                          | Zener Voltage (V_Z) (V)               | Zener Current (I_Z) (mA)           |  |  |

| 1                                                              | 0.0                                               |                                       | 0.0                                |  |  |

| 2                                                              | 1.0                                               |                                       |                                    |  |  |

| 3                                                              | 2.0                                               |                                       |                                    |  |  |

| 4                                                              | 3.0                                               |                                       |                                    |  |  |

| 5                                                              | 4.0                                               |                                       |                                    |  |  |

| 6                                                              | 5.0                                               |                                       |                                    |  |  |

| 7                                                              | 6.0                                               |                                       |                                    |  |  |

| 8                                                              | 7.0                                               |                                       |                                    |  |  |

| 9                                                              | 8.0                                               |                                       |                                    |  |  |

| 10                                                             | 9.0                                               |                                       |                                    |  |  |

|                                                                |                                                   |                                       |                                    |  |  |

| Export                                                         | to Sheets                                         |                                       |                                    |  |  |

| •                                                              | Observed Zener Breakdov                           | vn Voltage (V_Z):                     | V (from graph plotting)            |  |  |

| Observation Table 1.3: Half-Wave Rectifier Circuit Performance |                                                   |                                       |                                    |  |  |

| S.<br>No.                                                      | Input AC (Transformer Secondary)                  | Output (Across R_L)                   |                                    |  |  |

|                                                                | V_m (Peak Voltage) (V)                            | V_p(out) (Peak Output<br>Voltage) (V) | V_DC (Average Output)<br>(V) (DMM) |  |  |

| 1                                                              |                                                   |                                       |                                    |  |  |

| 2                                                              |                                                   |                                       |                                    |  |  |

| Export to Sheets                                               |                                                   |                                       |                                    |  |  |

| •                                                              | Observed Input Frequence Observed Output Ripple F | y (f_in): Hz<br>Frequency (f_ripple): | Hz                                 |  |  |

- Sketch Input Waveform (Time vs Voltage): (Draw a clean sine wave indicating V\_m and period)

- Sketch Output Waveform (Time vs Voltage): (Draw a half-wave rectified waveform indicating V\_p(out) and ripple)

# **Observation Table 1.4: Full-Wave Bridge Rectifier Circuit Performance**

| 187741 4  | E-14   | ^    |         |

|-----------|--------|------|---------|

| Without   | HIITER | Cana | icitor: |

| TTICITOUL |        | Cupu |         |

| S.<br>No. | Input AC (Transformer Secondary)                                                                                                   | Output (Across R_L) -<br>Unfiltered                         |                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------|

|           | V_m (Peak Voltage) (V)                                                                                                             | V_p(out) (Peak Output<br>Voltage) (V)                       | V_DC (Average Output)<br>(V) (DMM) |

| 1         |                                                                                                                                    |                                                             |                                    |

| 2         |                                                                                                                                    |                                                             |                                    |

| Export    | to Sheets                                                                                                                          |                                                             |                                    |

|           | Observed Output Ripple F<br>Sketch Input Waveform (T<br>V_m and period)<br>Sketch Output Waveform<br>rectified waveform indicating | ime vs Voltage): (Draw a cl<br>(Time vs Voltage) - Unfilter | ean sine wave indicating           |

| With F    | Filter Capacitor (C =                                                                                                              | μF):                                                        |                                    |

| S.<br>No. | Input AC (Transformer Secondary)                                                                                                   | Output (Across R_L) - Filtered                              |                                    |

|           | V_m (Peak Voltage) (V)                                                                                                             | V_p(out) (Peak Output<br>Voltage) (V)                       | V_DC (Average Output)<br>(V) (DMM) |

| 1         |                                                                                                                                    |                                                             |                                    |

| 2         |                                                                                                                                    |                                                             |                                    |

| Export    | t to Sheets                                                                                                                        |                                                             |                                    |

| •         | Observed Peak-to-Peak R<br>oscilloscope)<br>Sketch Output Waveform<br>DC waveform with reduced                                     | (Time vs Voltage) - Filtered                                |                                    |

| Obser     | vation Table 1.5: Zener Vol                                                                                                        | tage Regulator - Load Reg                                   | ulation Test                       |

| S.<br>No. |                            | Load Current (I_L) =<br>V_out/R_L (mA) | Output Voltage (V_out)<br>(V) (DMM) |

|-----------|----------------------------|----------------------------------------|-------------------------------------|

| 1         | Open Circuit (infty)       | 0                                      | V_NL =                              |

| 2         | 10k                        |                                        |                                     |

| 3         | 5k                         |                                        |                                     |

| 4         | 2k                         |                                        |                                     |

| 5         | 1k                         |                                        |                                     |

| 6         | 500                        |                                        |                                     |

| 7         | 200                        |                                        |                                     |

| 8         | 100                        |                                        |                                     |

|           |                            |                                        |                                     |

| Last      | (Minimum<br>Regulated R_L) | I_L(max) =                             | V_FL =                              |

| Export    | to Sheets                  |                                        |                                     |

| •         | Load Regulation Cal        | culation: Load Regulation ( =          | %                                   |

| Obser     | vation Table 1.6: Zene     | er Voltage Regulator - Line R          | Regulation Test                     |

| •         | Fixed Load Resistor        | ( <b>R_L</b> ): Ω                      |                                     |

| S. No     | . Input Voltage (V_ir      | n) (V) Output Voltage (V_c             | <b>put)</b> (V) (DMM)               |

| 1         | (Min Input, e.g., 10\      | <b>'</b> )                             |                                     |

| 2         |                            |                                        |                                     |

| 3         |                            |                                        |                                     |

| 4         | (Max Input, e.g., 15       | V)                                     |                                     |

| Export    | to Sheets                  |                                        |                                     |

| •         | Line Regulation Cald       | culation: Line Regulation ( = _        | %                                   |

|           |                            |                                        |                                     |

# 8.0 GRAPHS:

• Graph 1.1: I-V Characteristics of PN Junction Diode

- Plot I\_D (Y-axis) vs. V\_D (X-axis) for both forward and reverse bias from Table 1.1 on a single graph. Use appropriate scales (e.g., mA for forward current, μA for reverse current). Clearly mark the cut-in voltage.

- Graph 1.2: I-V Characteristics of Zener Diode in Reverse Bias

- Plot I\_Z (Y-axis) vs. V\_Z (X-axis) from Table 1.2. Clearly mark the Zener breakdown voltage (V Z).

#### 9.0 CALCULATIONS:

Show all your calculations clearly.

## 9.1 PN Junction Diode:

• From Graph 1.1, manually determine the cut-in voltage V\_F.

#### 9.2 Zener Diode:

From Graph 1.2, manually determine the Zener breakdown voltage V\_Z.

#### 9.3 Half-Wave Rectifier:

- Measured V\_m from oscilloscope.

- Measured V\_p(out) from oscilloscope.

- Measured V\_DC from DMM.

- Compare with theoretical values (ideal case):

- Theoretical V\_p(out)=V\_m-V\_F (use your measured V\_F).

- Theoretical V\_DC=(V\_m-V\_F)/pi.

## 9.4 Full-Wave Bridge Rectifier:

- Measured V\_m from oscilloscope.

- Measured V p(out) (unfiltered) from oscilloscope.

- Measured V\_DC (unfiltered) from DMM.

- Measured V\_p(out) (filtered) from oscilloscope.

- Measured V\_DC (filtered) from DMM.

- Measured V r(p-p) (filtered) from oscilloscope.

- Compare with theoretical values (ideal case):

- Theoretical V\_p(out)=V\_m-2V\_F.

- Theoretical V DC=2(V m-2V F)/pi.

- Theoretical  $V_r(p-p)=V_DC/(f_rippletimesR_LtimesC)$  or  $V_r(p-p)=I_DC/(f_rippletimesC)$ . Use  $f_ripple=2timesf_in$ .

## 9.5 Zener Voltage Regulator Design (R\_S calculation):

- State your chosen V\_Z, V\_in(min), V\_in(max), I\_ZK, I\_ZM, I\_L(max).

- R\_S=fracV\_in(min)-V\_ZI\_ZK+I\_L(max) = [Your Calculation]

- Chosen standard R\_S value: [Your Value]

Maximum Zener power dissipation check:

P\_Z(max)=V\_ZtimesfracV\_in(max)-V\_ZR\_S = [Your Calculation] (Compare with Zener diode's power rating).

## 9.6 Zener Voltage Regulator Performance (from tables 1.5 and 1.6):

- Load Regulation: Load Regulation ( = [Your Calculation]

- Line Regulation: Line Regulation ( = [Your Calculation]

#### 10.0 RESULTS:

Present the main results obtained from the experiment clearly.

- PN Junction Diode (1N4007):

- Observed Cut-in Voltage (V\_F): [Your Value] V

- Zener Diode (e.g., 5.1V):

- Observed Zener Breakdown Voltage (V\_Z): [Your Value] V

- Half-Wave Rectifier:

- Measured V\_DC: [Your Value] V

- Observed Ripple Frequency: [Your Value] Hz

- Full-Wave Bridge Rectifier (without filter):

- Measured V\_DC: [Your Value] V

- o Observed Ripple Frequency: [Your Value] Hz

- Full-Wave Bridge Rectifier (with filter):

- Measured V\_DC: [Your Value] V

- Measured Peak-to-Peak Ripple Voltage: [Your Value] V

- Zener Voltage Regulator:

- Calculated Series Resistor (R\_S): [Your Value] Ω

- Load Regulation: [Your Value] %

- Line Regulation: [Your Value] %

#### 11.0 DISCUSSION AND ANALYSIS:

This is a critical section where you interpret your results, compare them with theoretical expectations, explain observed phenomena, and discuss any discrepancies.

### 1. PN Junction Diode Behavior:

- Describe the shape of the I-V graph for the PN junction diode. Why does the current rise exponentially in forward bias after V\_F?

- Why is the reverse current very small? What happens if the reverse voltage approaches the diode's reverse breakdown voltage?

- Compare your experimentally determined V\_F with the typical value for silicon diodes. Account for any minor differences.

### 2. Zener Diode Behavior:

- Describe the shape of the I-V graph for the Zener diode in reverse bias. How does it differ from a standard PN junction diode in this region?

- Explain the concept of Zener breakdown and how the diode maintains a constant voltage across its terminals once in breakdown.

- Compare your measured V\_Z with the nominal value of the Zener diode you used.

## 3. Rectifier Performance Comparison:

- Visually compare the oscilloscope traces of the half-wave, unfiltered full-wave, and filtered full-wave rectifier outputs. Comment on the key differences (e.g., pulse frequency, DC level, ripple magnitude).

- Quantitatively compare the measured V\_DC and ripple characteristics for each rectifier type.

- Explain why the full-wave rectifier is generally preferred over the half-wave rectifier for power supply applications.

- Discuss the effectiveness of the filter capacitor in smoothing the DC output.

How does the ripple voltage relate to the capacitor value and load current?

## 4. Zener Voltage Regulator Performance:

- Explain how the Zener diode regulates the output voltage despite variations in input voltage (line regulation) and load current (load regulation).

- Analyze your calculated load regulation and line regulation percentages. Are these values acceptable for the application of a simple voltage regulator? What do these percentages indicate about the regulator's stability?

- Discuss the limitations of a simple Zener regulator (e.g., efficiency, current capacity, precise regulation, temperature effects). What are the advantages of using it for small power applications?

- Could this Zener regulator be used directly after an unfiltered half-wave rectifier? Why or why not?

#### 5. Sources of Error:

- Identify potential sources of experimental error (e.g., component tolerances, meter inaccuracies, oscilloscope calibration, breadboard contact issues, heat effects on diodes).

- How might these errors have influenced your results?

#### 12.0 CONCLUSION:

Conclude your experiment by summarizing the key learning outcomes.

This experiment successfully demonstrated the fundamental characteristics of PN junction and Zener diodes. We observed the unidirectional current flow in PN junction diodes and the voltage regulation capability of Zener diodes in reverse breakdown. The rectification process was clearly understood by constructing and analyzing half-wave and full-wave bridge rectifiers, highlighting the superiority of full-wave rectification and the crucial role of filter capacitors in ripple reduction. Furthermore, the practical design and testing of a Zener voltage regulator provided insight into basic voltage stabilization principles and the concepts of line and load regulation. The experimental results generally aligned with theoretical predictions, with minor deviations attributed to non-ideal component behavior and

measurement limitations. This experiment has laid a strong foundation for understanding

more complex analog circuits.